# **ELECTRONIC CIRCUIT ANALYSIS**

**LABORATORY MANUAL(R22A0486)**

B.TECH (II YEAR – II SEM) (2024-25)

Prepared by Dr. Sadanand Yadav, Assistant Professor

**Department of Electronics and Communication Engineering**

# MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

(Autonomous Institution – UGC, Govt. of India)

Recognized under 2(f) and 12 (B) of UGC ACT 1956

Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – 'A' Grade - ISO 9001:2015 Certified)

Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India

# **ELECTRONICS & COMMUNICATION ENGINEERING**

# **VISION**

To provide high quality academic programmes, training activities, research facilities and opportunities supported by continuous industry institute interaction aimed at employability, entrepreneurship, leadership and research aptitude among students.

# **MISSION**

To evolve into a center of excellence in Engineering Technology through creative and innovative practices in teaching-learning, promoting academic achievement & research excellence to produce internationally accepted competitive and world class professionals.

# **QUALITY POLICY**

- Impart up-to-date knowledge to the students in Electronics & Communication area to make them quality engineers.

- Make the students experience the applications on quality equipment and tools.

- Provide systems, resources and training opportunities to achieve continuous improvement.

- Maintain global standards in education, training and services.

# ROGRAMME EDUCATIONAL OBJECTIVES (PEOs)

### PEO1: PROFESSIONALISM & CITIZENSHIP

To create and sustain a community of learning in which students acquire knowledge and learn to apply it professionally with due consideration for ethical, ecological and economic issues.

### PEO2: TECHNICAL ACCOMPLISHMENTS

To provide knowledge based services to satisfy the needs of society and the industry by providing hands on experience in various technologies in core field.

# PEO3: INVENTION, INNOVATION AND CREATIVITY

To make the students to design, experiment, analyze, interpret in the core field with the help of other multi disciplinary concepts wherever applicable.

# PEO4: PROFESSIONAL DEVELOPMENT

To educate the students to disseminate research findings with good soft skills and become a successful entrepreneur.

### PEO5: HUMAN RESOURCE DEVELOPMENT

To graduate the students in building national capabilities in technology, education and research.

# PROGRAMME SPECIFIC OBJECTIVES (PSOs)

# **PSO1**

To develop a student community who acquire knowledge by ethical learning and fulfill the societal and industry needs in various technologies of core field.

#### PSO<sub>2</sub>

To nurture the students in designing, analyzing and interpreting required in research and development with exposure in multi disciplinary technologies in order to mould them as successful industry ready engineers/entrepreneurs

#### **PSO3**

To empower students with all round capabilities who will be useful in making nation strong in technology, education and research domains.

# **PROGRAM OUTCOMES (POs)**

# **Engineering Graduates will be able to:**

- 1. **Engineering knowledge**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- 2. **Problem analysis**: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- 3. **Design / development of solutions**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- 4. **Conduct investigations of complex problems**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- 5. **Modern tool usage**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- 6. **The engineer and society**: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- 7. **Environment and sustainability**: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- 8. **Ethics**: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- 9. **Individual and team work**: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- 10. **Communication**: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- 11. **Project management and finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multi disciplinary environments.

- 12. Life- long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

# **Laboratory Rules**

#### **General Rules of Conduct in Laboratories:**

- 1. You are expected to arrive on time and not depart before the end of a laboratory.

- 2. You must not enter a lab unless you have permission from a technician or lecturer.

- 3. You are expected to comply with instructions, written or oral, that the laboratory Instructor gives you during the laboratory session.

- 4. You should behave in an orderly fashion always in the lab.

- 5. You must not stand on the stools or benches in the laboratory.

- 6. Keep the workbench tidy and do not place coats and bags on the benches.

- 7. You must ensure that at the end of the laboratory session all equipment used is stored away where you found it.

- 8. You must put all rubbish such as paper outside in the corridor bins. Broken components should be returned to the lab technician for safe disposal.

- 9. You must not remove test equipment, test leads or power cables from any lab without permission.

- 10. Eating, smoking and drinking in the laboratories are forbidden.

- 11. The use of mobile phones during laboratory sessions is forbidden.

- 12. The use of email or messaging software for personal communications during laboratory sessions is forbidden.

- 13. Playing computer games in laboratories is forbidden.

### **Specific Safety Rules for Laboratories:**

- 1. You must not damage or tamper with the equipment or leads.

- 2. You should inspect laboratory equipment for visible damage before using it. If there is a problem with a piece of equipment, report it to the technician or lecturer. DONOT return equipment to a storage area

- 3. You should not work on circuits where the supply voltage exceeds 40 volts without very specific approval from your lab supervisor. If you need to work on such circuits, you should contact your supervisor for approval and instruction on how to do this safely before commencing the work.

| 4. Always use an appropriate stand for holding your soldering iron.                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| 5. Turn off your soldering iron if it is unlikely to be used for more than 10 minutes.                                                      |

| 6. Never leave a hot soldering iron unattended.                                                                                             |

| 7. Never touch a soldering iron element or bit unless the iron has been disconnected from the mains and has had adequate time to cool down. |

| 8. Never strip insulation from a wire with your teeth or a knife, always use an appropriate wire stripping tool.                            |

| 9. Shield wire with your hands when cutting it with a pliers to prevent bits of wire flying about the bench.                                |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

# MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY II Year B.Tech. ECE- II Sem

L/T/P/C -/-/2/1

# (R22A0486) ELECTRONIC CIRCUIT ANALYSIS LABARATORY

#### **Course Outcomes:**

# Upon completing this course, the students will be able to

- 1. Design power amplifiers and find its efficiency

- 2. Design tuned amplifiers and find its Q-factor

- 3. Design various multivibrators and sweep circuits. Understand the necessity of linearity

- 4. Design Bootstrap and understanding the concepts of frequency division

# **List of Experiments:**

# **CYCLE-I: Hardware Laboratory (Minimum eight experiments)**

- 1. Design transformer coupled class A power amplifier and draw the input and output waveforms Find its efficiency

- 2. Design class B power amplifier and draw the input and output waveforms, find 2nd order and above harmonics.

- 3. Prove that the complementary symmetry push pull eliminates cross over distortion.

- 4. Design class C power amplifier and draw the input and output waveforms

- 5. Design a single tuned amplifier and determine the Q of its tuned circuit practically.

- 6. Design a Bistable Multivibrator and analyze the effect of commutating capacitors and Draw the wave forms at base and collector of transistors.

- 7. Design an Astable Multivibrator and draw the wave forms at base and collector of Transistors.

- 8. Design a Monostable Multivibrator and draw the input and output waveforms

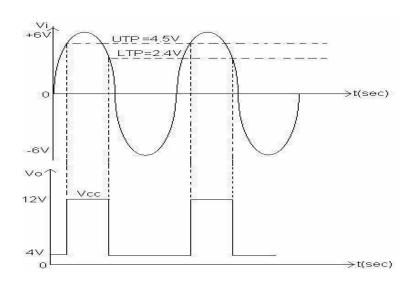

- 9. Draw the response of Schmitt trigger for gain of greater than and less than one.

- 10. Design a Bootstrap sweep circuit using BJT and draw its output time base waveform

# CYCLE-II: Design and Simulation in Simulation Laboratory using any Simulation Software. (Minimum eight experiments)

- 1. Common Emitter Amplifier

- 2. Common Source Amplifier

- 3. Two stage RC-Coupled amplifier

- 4. Current Shunt Voltage Feedback amplifier

- 5. Cascade Amplifier

- 6. Class A Power Amplifier

- 7. Switching Characteristics of a Transistor

- 8. Design a Bistable Multivibrator and draw its waveforms

- 9. Design a Astable Multivibrator and draw its waveforms

- 10. Design a Monostable Multivibrator and draw its waveforms

### **Major Equipment required for Laboratories:**

- 1. Computer System with latest specifications connected

- 2. Window XP or equivalent

- 3. Simulation software-Multisim or any equivalent simulation software

- 4. Regulated Power Suppliers, 0-30V 5. 20 MHz, Dual Channel Cathode Ray Oscilloscopes.

- 6. Functions Generators-Sine and Square wave signals

- 7. Multimeters

- 8. Electronic Component

# EXPERIMENT NO: 1 COMMON EMITTER AMPLIFIER

#### AIM:

To determine the gain and bandwidth of a CE Amplifier from its frequency response curve.

**SOFTWARE REQUIRED:** Multisim

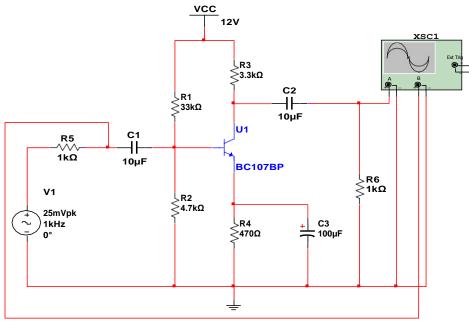

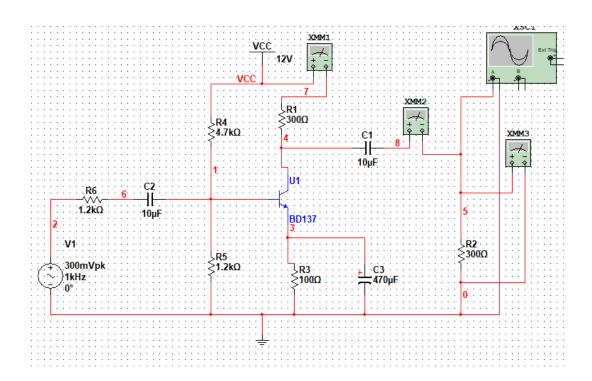

**CIRCUIT DIAGRAM:**

#### THEORY:

The single stage common emitter amplifier circuit shown above uses what is commonly called "Voltage Divider Biasing" or "self biasing". This type of biasing arrangement uses two resistors as a potential divider network and is commonly used in the design of bipolar transistor amplifier circuits. This type of biasing arrangement greatly reduces the effects of varying Beta,  $(\beta)$  by holding the Base bias at a constant steady voltage. This type of biasing produces the greatest stability.

The Common Emitter Amplifier circuit has a resistor in its Collector circuit. The current flowing through this resistor produces the voltage output of the amplifier. The value of this resistor is chosen so that at the amplifiers quiescent operating point, Q-point this output voltage lies half way along the transistors load line. In Common Emitter Amplifier circuits, capacitors C1 and C2 are used as Coupling Capacitors to separate the AC signals from the DC biasing voltage. This ensures that the bias condition set up for the circuit to operate correctly is not affected by any additional amplifier stages, as the capacitors will only pass AC signals and block any DC component.

The output AC signal is then superimposed on the biasing of the following stages. Also a bypass capacitor, CE is included in the Emitter leg circuit. This capacitor is an open circuit component for DC bias meaning that the biasing currents and voltages are not affected by the addition of the capacitor maintaining a good Q-point stability. However, this bypass capacitor short circuits the Emitter resistor at high frequency signals and only RL plus a very small internal resistance acts as the transistors load increasing the voltage gain to its maximum.

Generally, the value of the bypass capacitor, CE is chosen to provide a reactance of at most, 1/10th the value of RE at the lowest operating signal frequency. A single stage Common Emitter Amplifier is also an "Inverting Amplifier" as an increase in Base voltage causes a decrease in V

out and a decrease in Base voltage produces an increase in Vout. The output signal is 180° out of phase with the input signal.

#### PROCEDURE:

- 1. Open the multisim icon in the system.

- 2. Place all the necessary components required for the design of the CE amplifier circuit i.e. Resistors, Capacitors, Transistors, Voltage sources, Power sources, Ground etc on the design window.

- 3. Connect all the components by proper wiring and also assure that nodes are formed at the interconnection points.

- 4. Connect the two channels of the Oscilloscope to input and output of the circuit and by using the simulation switch and check the input and output waveforms.

- 5. Assign net numbers to input and output wires by double clicking on the particular wire and clicking on the show option.

- 6. To observe the frequency response, go to simulate malysis and select the start and stop frequencies, select vertical scale as decibels, specify the output variables and click on simulate.

- 7. A window opens showing the frequency response on the top and phase response at the bottom.

- 8. From the frequency response, calculate the bandwidth of the Amplifier.

- 9. To obtain the netlist, go to transfer ---- proper netlist and save the netlist in a text file. On opening the text file from the saved location, a netlist is obtained containing the specifications of all the used components used in the design of the circuit.

#### **OBSERVATION TABLE:**

| C No | Fraguanau/h=\ | Output valtaga(va) | Valtage gain | Cain (db)           |

|------|---------------|--------------------|--------------|---------------------|

| S.No | Frequency(hz) | Output voltage(vo) | Voltage gain | Gain (db)           |

|      |               |                    | (vo/vi)      | Avf=20 log (vo/vi). |

|      |               |                    |              |                     |

|      |               |                    |              |                     |

|      |               |                    |              |                     |

|      |               |                    |              |                     |

|      |               |                    |              |                     |

|      |               |                    |              |                     |

|      |               |                    |              |                     |

|      |               |                    |              |                     |

|      |               |                    |              |                     |

Bandwidth of the CE amplifier =  $f_h$ - $f_l$  HZ

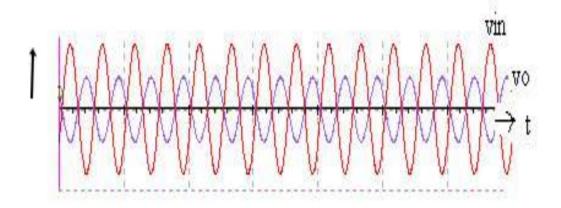

### **EXPECTED GRAPH:**

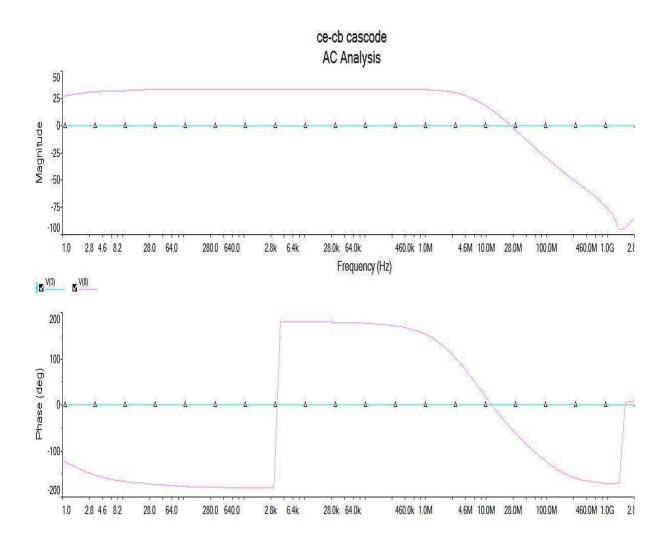

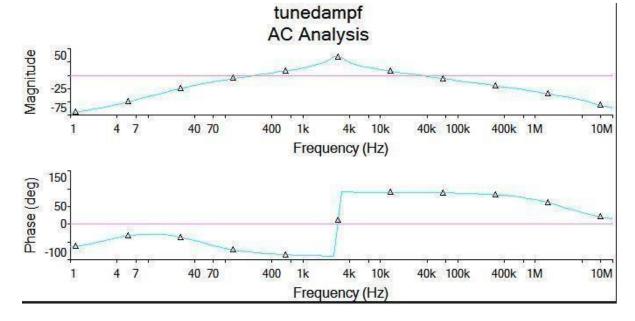

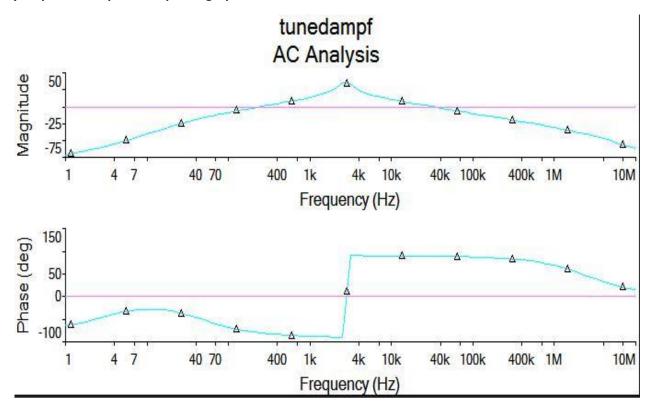

# FREQUENCY RESPONSE AND PHASE RESPONSE GRAPHS

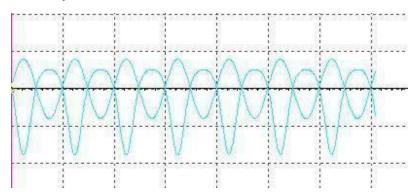

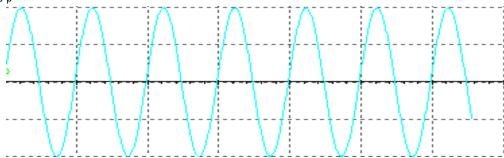

### **INPUT Vs OUTPUT WAVEFORM**

#### **RESULT:**

| The maximum gain is | dB and bandwidth is | Hz of the CE Amplifier |

|---------------------|---------------------|------------------------|

|                     |                     |                        |

# QUESTIONS:

- 1. What is the phase difference between input and output waveforms of CE amplifier?

- 2. What type of biasing is used in the given circuit?

- 3. If the given transistor is replaced by P-N-P, can we get the output or not?

- 4. What is the effect of emitter bypass capacitor on frequency response?

- 5. What is the effect of coupling capacitor?

- 6. What is the region of transistor so that it operates as an amplifier?

- 7. Draw the h-parameter model of CE amplifier.

- 8. How does transistor acts as an amplifier.

- 9. Mention the characteristics of CE amplifier.

# **Exercise Question:**

- 1. Find the frequency response of CE Amplifier by changing the bypass capacitor value.

- 2. Find the frequency response of CE Amplifier by removing the bypass capacitor.

#### **OBSERVATIONS:**

ECE, MRCET **EDC Manual**

**EDC Manual** ECE, MRCET TITLE NAME DATE

# EXPERIMENT NO: 2 COMMON SOURCE AMPLIFIER

#### AIM:

To determine the Band width from the frequency response of the common source FET Amplifier.

**SOFTWARE REQUIRED: Multisim**

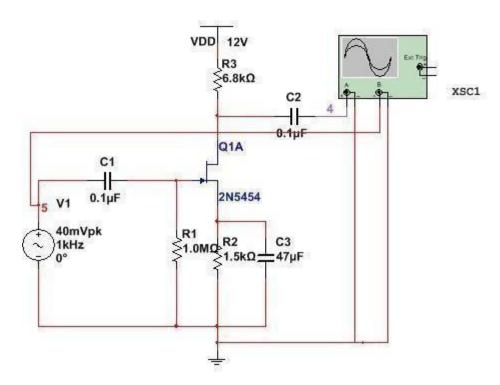

#### **CIRCUIT DIAGRAM:**

### THEORY:

A field-effect transistor (FET) is a type of transistor commonly used for weak-signal amplification (for example, for amplifying wireless (signals). The device can amplify analog or digital signals. It can also switch DC or function as an oscillator. In the FET, current flows along a semiconductor path called the channel. At one end of the channel, there is an electrode called the source. At the other end of the channel, there is an electrode called the drain. The physical diameter of the channel is fixed, but its effective electrical diameter can be varied by the application of a voltage to a control electrode called the gate. Field-effect transistors exist in two major classifications. These are known as the junction FET (JFET) and the metal-oxide-semiconductor FET (MOSFET). The junction FET has a channel consisting of N-type semiconductor (N-channel) or P-type semiconductor (P-channel) material; the gate is made of the opposite semiconductor type. In P-type material, electric charges are carried mainly in the form of electron deficiencies called holes.

In N-type material, the charge carriers are primarily electrons. In a JFET, the junction is the boundary between the channel and the gate. Normally, this P -N junction is reverse-biased (a DC voltage is applied to it) so that no current flows between the channel and the gate.

However, under some conditions there is a small current through the junction during part of the input signal cycle.

The FET has some advantages and some disadvantages relative to the bipolar transistor. Field-effect transistors are preferred for weak-signal work, for example in wireless, communications and broadcast receivers. They are also preferred in circuits and systems requiring high impedance. The FET is not, in general, used for high-power amplification, such as is required in large wireless communications and broadcast transmitters.

Field-effect transistors are fabricated onto silicon integrated circuit (IC) chips. A single IC can contain many thousands of FETs, along with other components such as resistors, capacitors, and diodes. A common source amplifier FET amplifier has high input impedance and a moderate voltage gain. Also, the input and output voltages are 180 degrees out of Phase.

#### PROCEDURE:

- 1. Open the multisim icon in the system.

- 2. Place all the necessary components required for the design of the CS FET amplifier circuit i.e. Resistors, Capacitors, Transistors, Voltage sources, Power sources, Ground etc on the design window. Connect all the components by proper wiring and also assure that nodes are formed at the interconnection points.

- 3. Connect the two channels of the Oscilloscope to input and output of the circuit and by using the simulation switch and check the input and output waveforms.

- 4. Assign net numbers to input and output wires by double clicking on the particular wire and clicking on the show option.

- 5. To observe the frequency response, go to simulate hallysis and select the start and stop frequencies, select vertical scale as decibels, specify the output variables and click on simulate.

- 6.A window opens showing the frequency response on the top and phase response at the bottom.

- 7. From the frequency response, calculate the bandwidth of the Amplifier.

- 8. To obtain the netlist, go to transfer ---- prort netlist and save the netlist in a text file. On opening the text file from the saved location, a netlist is obtained containing the specifications of all the used components used in the design of the circuit containing the specifications of all the used components used in the design of the circuit.

#### **OBSERVATION TABLE:**

| S.No | Frequency(hz) | Output voltage(vo) | Voltage gain (vo/vi) | Gain (db)<br>Avf=20 log (vo/vi). |

|------|---------------|--------------------|----------------------|----------------------------------|

|      |               |                    |                      |                                  |

|      |               |                    |                      |                                  |

|      |               |                    |                      |                                  |

|      |               |                    |                      |                                  |

|      |               |                    |                      |                                  |

Bandwidth of the CE-CB Cascode amplifier=f<sub>h\_\_\_\_fl</sub> Hz

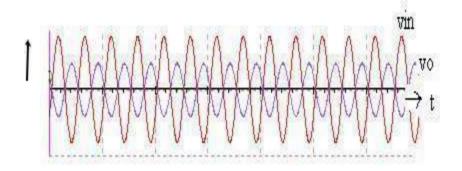

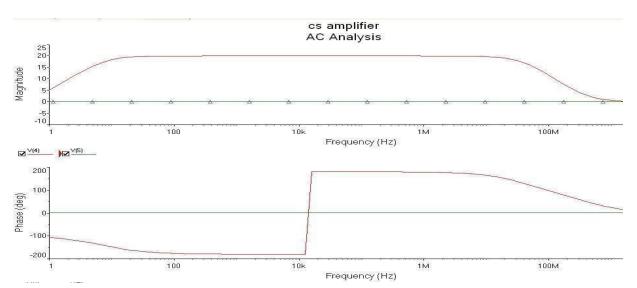

### **MODEL GRAPH:**

# **Input vs Output Waveforms**

#### **FREQUENCY RESPONSE:**

**RESULT:** We have obtained the frequency response of the common Source FET Amplifier and also found its Bandwidth to be\_\_\_\_\_Hz.

### **QUESTIONS:**

- 1. How does FET acts as an amplifier?

- 2. What are the parameters of a FET?

- 3. What is an amplification factor?

- 4. Draw the h-parameter model of the FET.

- 5. What are the advantages of FET over BJT?

- 6. What is the region of FET so that it acts as an amplifier?

- 7. What are the differences between JFET and MOSFET?

- 8. What type of biasing is used in the given circuit?

#### **Exercise Question:**

- 1. Find the frequency response of CS Amplifier by changing the bypass capacitor value.

- 2. Find the frequency response of CS Amplifier by removing the bypass capacitor.

# **OBSERVATIONS:**

ECE, MRCET **EDC Manual**

**EDC Manual** ECE, MRCET TITLE NAME DATE

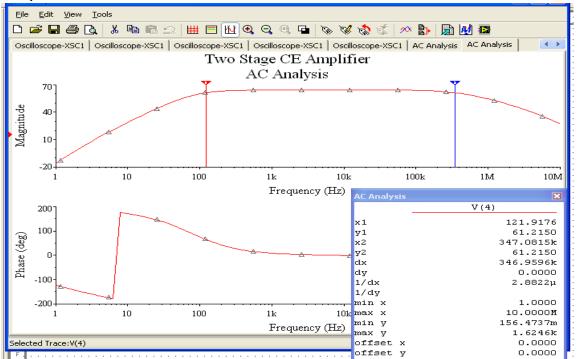

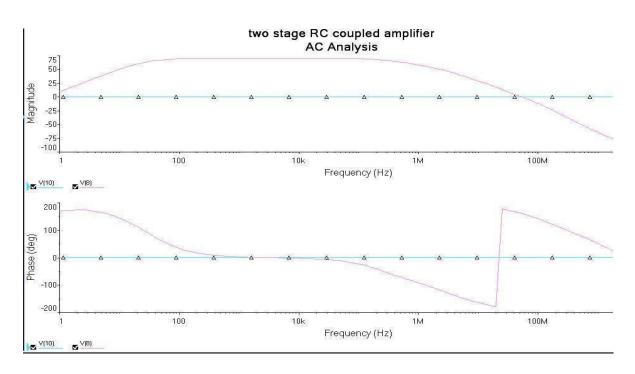

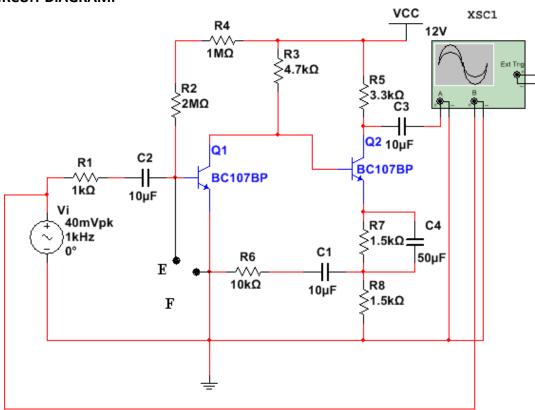

# EXPERIMENT NO: 3 TWO STAGE RC-COUPLED AMPLIFIER

#### AIM:

To study the response of a two stage RC-coupled amplifier and calculate gain and band width.

#### **SOFTWARE REQUIRED: Multisim**

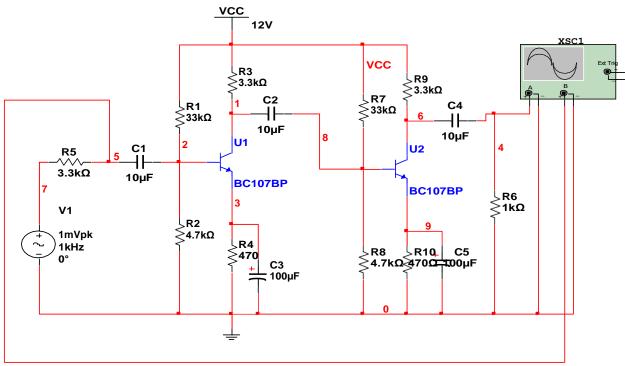

#### **CIRCUIT DIAGRAM:**

#### THEORY:

As the gain provided by a single stage amplifier is usually not sufficient to drive the load, so to achieve extra gain multi-stage amplifier are used. In multi-stage amplifiers output of one-stage is coupled to the input of the next stage. The coupling of one stage to another is done with the help of some coupling devices. If it is coupled by RC then the amplifier is called RC -coupled amplifier. Frequency response of an amplifier is defined as the variation of gain with respective frequency. The gain of the amplifier increases as the frequency increases from zero till it becomes maximum at lower cut-off frequency and remains constant till higher cut-off frequency and then it falls again as the frequency increases. At low frequencies the reactance of coupling capacitor C<sub>C</sub> is quite high and hence very small part of signal will pass through from one stage to the next stage.

#### **APPLICATIONS:**

- 1. Audio amplifiers

- Radio Transmitters and Receivers.

#### PROCEDURE:

- 1. Open the multisim icon in the system.

- 2. Place all the necessary components required for the design of the two stage RCCoupled amplifier circuit i.e. Resistors, Capacitors, Transistors.

- 3. Voltage sources, Power sources, Ground etc on the designwindow.

- 4. Connect all the components by proper wiring and also assure that nodes are formedat the interconnection points.

- 5. Connect the two channels of the Oscilloscope to input and output of the circuit and by using the simulation switch and check the input and output waveforms.

- 6. Assign net numbers to input and output wires by double clicking on the particular wire and clicking on the show option.

- 7. To observe the frequency response, go to simulate----- malysis ------- analysis and select the start and stop frequencies, select vertical scale as decibels, specify the output variables and click on simulate.

- 8. A window opens showing the frequency response on the top and phase response at the bottom.

- 9. From the frequency response, calculate the bandwidth of the Amplifier.

- 10. To obtain the netlist, go to transfer ---- port netlist and save the netlist in a text file. On opening the text file from the saved location, a netlist is obtained containing the specifications of all the used components used in the design of the circuit.

### **OBSERVATION TABLE:**

| S.No | Frequency(hz) | Output      | Voltage gain (vo/vi) | Gain (db)           |

|------|---------------|-------------|----------------------|---------------------|

|      |               | voltage(vo) |                      | Avf=20 log (vo/vi). |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

|      |               |             |                      |                     |

Bandwidth of the CE-CB Cascode amplifier=f<sub>h</sub>-f<sub>l</sub>Hz

### **CALCULATIONS:**

- 1. Determine lower cut-off frequency and upper cut-off frequency from the graph.

- 2. Calculate Band width.

#### **EXPECTED GRAPH:**

# **Frequency Response:**

#### **RESULT:**

The maximum gain is \_\_\_\_\_dB and bandwidth is \_\_\_\_\_Hz of the CE Amplifier.

### **QUESTIONS:**

- 1. What are the advantages and disadvantages of multi-stage amplifiers?

- 2. Why gain falls at HF and LF?

- 3. Why the gain remains constant at MF?

- 4. Explain the function of emitter bypass capacitor, CE?

- 5. How the band width will be affected as more number of stages are cascaded?

- 6. Define frequency response?

- 7. Give the formula for effective lower cut-off frequency, when N-number of stages is cascaded.

### **Exercise Question:**

Find the frequency response of 2 Stage CE Amplifier by changing the coupling capacitor to

- i) Direct coupling

- ii) Transformer coupling

# **OBSERVATIONS:**

ECE, MRCET **EDC Manual**

**EDC Manual** ECE, MRCET TITLE NAME DATE

# EXPERIMENT NO: 4 CURRENT SHUNT FEEDBACK AMPLIFIER

### AIM:

To determine the effect of feedback on the frequency response of a current shunt feedback amplifier.

**SOFTWARE REQUIRED:** Multisim

#### **CIRCUIT DIAGRAM:**

#### PROCEDURE:

### TO DETERMINE THE FREQUENCY RESPONSE WITH FEEDBACK

- 1. Open the multisim icon in the system.

- 2. Place all the necessary components required for the design of the current shunt feedback amplifier circuit i.e. Resistors, Capacitors, Diodes, Transistors, Voltage sources, Power sources, Ground etc on the design window.

- 3. Connect all the components by proper wiring and also assure that nodes are formed at the interconnection points.

- 3. Connect the channel of the Oscilloscope to the output of the circuit and by using the simulation switch and check output waveform.

- 4. To obtain the netlist, go to transfer port netlist and save the netlist in a text file. On opening the text file from the saved location, a netlist is obtained containing the specifications of all the used components used in the design of the circuit.

- 5. Vary the input frequency from 10Hz to 1MHz with input voltage constant (40mvpp) and note down the output voltage.

- 6. Calculate the voltage gain in dB using the formula Av=20 log(Vo/Vi).

# TO DETERMINE THE FREQUENCY RESPONSE WITH FEEDBACK

- 1. Now connect E-F terminals in the circuit.

- 2. Connect the output of the feedback amplifier to the other channel of the CRO.

- 3. Vary the input frequency from 10Hz to 1MHz with input voltage constant (40mvpp) and note down the output voltage.

- 4. Calculate the voltage gain in dB using the formula Av=20 log (Vo/Vi).

### **OBSERVATIONS TABLE**

#### 1. WITHOUT FEEDBACK

Vi= 40mvp-p at 1kHz

| S.No | Frequency(hz) | Output voltage(vo) | Voltage gain<br>(vo/vi) | Gain (db)<br>Avf=20 log (vo/vi). |

|------|---------------|--------------------|-------------------------|----------------------------------|

|      |               |                    |                         |                                  |

|      |               |                    |                         |                                  |

|      |               |                    |                         |                                  |

|      |               |                    |                         |                                  |

|      |               |                    |                         |                                  |

Bandwidth without feedback=-----

#### 2. WITH FEEDBACK

Vi= 40mvp-p at 1kHz

| S.NO | Frequency(hz) | Output voltage<br>(vo) | Voltage gain (avf=vo/vi) | Gain (db)<br>Avf=20 log (vo/vi). |

|------|---------------|------------------------|--------------------------|----------------------------------|

|      |               |                        |                          |                                  |

|      |               |                        |                          |                                  |

|      |               |                        |                          |                                  |

|      |               |                        |                          |                                  |

Bandwidth with feedback = ------

#### **EXPECTED GRAPH:**

# **RESULT:**

The Av of the current shunt feedback amplifier is\_\_\_\_\_and the bandwidth is\_\_\_\_\_without feedback and The Av of the current shunt feedback amplifier is\_\_\_\_and the bandwidth is\_\_\_\_with feedback.

# **QUESTIONS:**

- 1. What is feedback?

- 2. What are the characteristics of feedback?

- 3. What is meant by sampling and mixing?

- 4. What are the configurations of feedback amplifiers?

- 5. What is the effect of feedback on an amplifier?

- 6. What is the effect of feedback on input and output resistances?

# **Exercise Question:**

1. Determine the input resistance ,Output resistance of Current Shut Feedback amplifier with and without feedback?

# **OBSERVATIONS:**

ECE, MRCET **EDC Manual**

**EDC Manual** ECE, MRCET TITLE NAME DATE

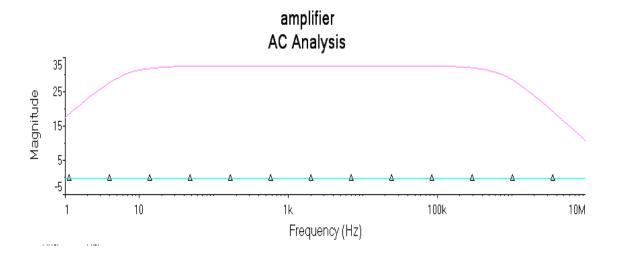

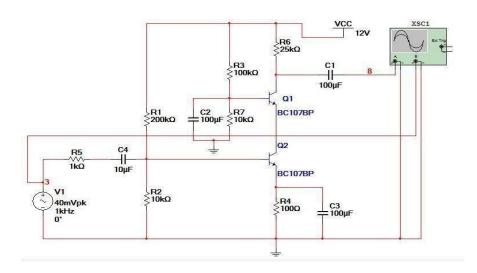

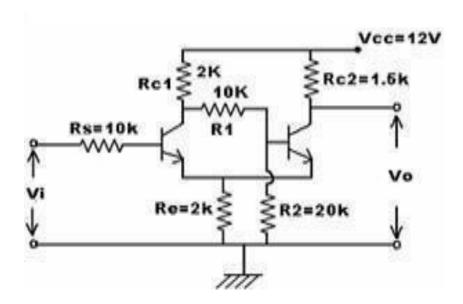

# EXPERIMENT NO: 5 CE-CB CASCODE AMPLIFIER

#### AIM:

To determine the gain and bandwidth of a CE –CB Cascode Amplifier from its frequency response curve.

**SOFTWARE REQUIRED: Multisim**

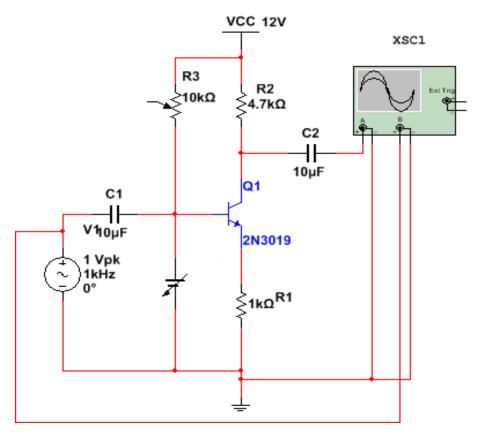

**CIRCUIT DIAGRAM:**

#### THEORY:

A Cascode amplifier consists of a common-emitter stage loaded by the emitter of a common-base stage. While the C-B (common-base) amplifier is known for wider bandwidth than the C-E (common-emitter) configuration, the low input impedance (10s of  $\Omega$ ) of C-B is a limitation for many applications. The solution is to precede the C-B stage by a low gain C-E stage which has moderately high input impedance ( $k\Omega s$ ). The stages are in a cascode configuration, stacked in series, as opposed to cascaded for a standard amplifier chain. The cascode amplifier configuration has both wide bandwidth and moderately high input impedance. Before the invention of the RF dual gate MOSFET, the BJT Cascode amplifier could have been found in UHF (ultra high frequency) TV tuners. A Cascode amplifier has a high gain, moderately high input impedance, high output impedance, and a high bandwidth.

#### PROCEDURE:

- 1. Open the multisim icon in the system.

- 2. Place all the necessary components required for the design of the CE -CB cascode amplifier circuit i.e Resistors, Capacitors, Transistors, Voltage sources, Power sources, Ground etc on the design window.

- 3. Connect all the components by proper wiring and also assure that nodes are formed at the interconnection points.

- 4. Connect the two channels of the Oscilloscope to input and output of the circuit and by using the simulation switch and check the input and output waveforms.

- 5. Assign net numbers to input and output wires by double clicking on the particular wire and clicking on the show option.

- 6. To observe the frequency response, go to simulate----- **>** analysis ----- analysis and selectthe start and stop frequencies, select vertical scale as decibels, specify the output variables and click on simulate.

- 7. A window opens showing the frequency response on the top and phase response at the bottom.

- 8. From the frequency response, calculate the bandwidth of the Amplifier.

- 9. To obtain the net list, go to transfer ---- port netlist and save the net list in text file. On opening the text file from the saved location, a netlist is obtained containing the specifications of all the used components used in the design of the circuit.

#### **OBSERVATION TABLE:**

| S.NO | FREQUENCY(Hz) | GAIN(dB) |

|------|---------------|----------|

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

Bandwidth of the CE-CB Cascode amplifier=f<sub>h</sub>-f<sub>l</sub>Hz

# **EXPECTED GRAPH:**

# **Input Vs Output waveforms**

#### REQUENCY RESPONSE AND PHASE RESPONSE GRAPHS

#### **RESULT:**

The maximum gain is \_\_\_\_\_dB and bandwidth is \_\_\_\_\_Hz of the CE - CB Cascode Amplifier.

#### **QUESTIONS:**

- 1. What is the difference between cascading and cascading?

- 2. What are the advantages of cascading?

- 3. What is the upper and lower cutoff frequencies of an n-stage cascaded amplifier?

- 4. What is the effective bandwidth of an n-stage Cascaded amplifier?

- 5. What is the preferred amplifier configuration for input stage in a cascade amplifier?

#### **Exercise Question:**

1. Observe the Frequency response and bandwidth of n Stage cascaded amplifier?

# **OBSERVATIONS:**

ECE, MRCET **EDC Manual**

**EDC Manual** ECE, MRCET TITLE NAME DATE

# **EXPERIMENT NO: 6 CLASS-A POWER AMPLIFIER**

#### AIM:

To design a series fed class-A power amplifier in order to achieve max output ac power and efficiency.

**EQUIPMENT REQUIRED:** Multisim

**CIRCUIT DIAGRAM:**

#### THEORY:

The above circuit is called as "series fed" because the load RL is connected in series with transistor output. It is also called as direct coupled amplifier.

ICQ = Zero signal collector current

VCEQ = Zero signal collector to emitter voltage

Power amplifiers are mainly used to deliver more power to the load. To deliver more power it requires large input signals, so generally power amplifiers are preceded by a series of voltage amplifiers. In class-A power amplifiers, Q-point is located in the middle of DC-load line. So output current flows for complete cycle of input signal. Under zero signal condition, maximum power dissipation occurs across the transistor. As the input signal amplitude increases power dissipation reduces The maximum theoretical efficiency is 25%.

#### **APPLICATIONS:**

This is used for low power linear applications in audio and wideband RF range, where high efficiency is not required.

# **EXTENSIONS:**

In series fed class-A power amplifier we have calculated the efficiency i.e. how efficiently DC-power is converted into AC-power depending on the magnitude of input signal. Once we design a power amplifier for a particular efficiency, the circuit will not give that efficiency to all its

input signals of different amplitudes. Hence, depending on the input signal we have to choose Vcc to obtain a particular efficiency. By employing Transformer coupling, efficiency can be improved to 50%. The experiment is conducted using low power transistors like BC107, SL100 only to get familiarity in biasing and measurement. Actual power amplifiers operate at 1 watt to 100 watts. This will call for operating transistors high current and small value resistors of greater than 1/4 to 1 watt which are used in the laboratory. Actual power amplifiers use heat sinks on the transistors.

#### PROCEDURE:

- 1. Open the multisim icon in the system.

- 2. Place all the necessary components required for the design of the Complementary symmetry Class B Power amplifier circuit i.e. Resistors, Capacitors, Diodes, Transistors, Voltage sources, Power sources, Ground etc on the designwindow.

- 3. Connect all the components by proper wiring and also assure that nodes are formed at the interconnection points.

- 4. Connect the channel of the Oscilloscope to the output of the circuit and by using the simulation switch and check output waveform.

- 5. To obtain the netlist, go to transfer port netlist and save the netlist in a text file. On opening the text file from the saved location, a netlist is obtained containing the specifications of all the used components used in the design of the circuit.

#### **OBSERVATIONS:**

Efficiency is defined as the ratio of AC output power to DC input power

DC input power =  $Vcc \times I_{CQ}$

AC output power =  $V_{p-p}^2 / 8R_1$

#### **CALCULATIONS:**

Under zero signal condition:

$Vcc = I_BR_B + V_{BE}$

$I_{BQ} = (V_{CC} - V_{BE}) / R_{B}$

$I_{CQ} = \beta \times I_{BQ}$

$V_{CE} = V_{CC} - I_{C}R_{C}$

# **EXPECTED GRAPH:**

| RESULT: |  |

|---------|--|

|         |  |

| 1. | 1. The maximum input signal amplitude which produces undistorted output signal is |                                           |  |

|----|-----------------------------------------------------------------------------------|-------------------------------------------|--|

| 2. | The practical efficiency of the circuit is                                        |                                           |  |

| 3. | The efficiency observed is                                                        | against theoretical maximum of 25%, Since |  |

## **QUESTIONS:**

- 1. Differentiate between voltage amplifier and power amplifier

- 2. Why power amplifiers are considered as large signal amplifier?

- 3. When does maximum power dissipation happen in this circuit?

- 4. What is the maximum theoretical efficiency?

- 5. Sketch wave form of output current with respective input signal.

- 6. What are the different types of class-A power amplifiers available?

- 7. What is the theoretical efficiency of the transformer coupled class-A power amplifier?

- 8. What is difference in AC, DC load line?

- 9. How do you locate the Q-point?

- 10. What are the applications of class-A power amplifier?

# **Exercise Question:**

1. Try to increase the efficiency of Class A power amplifier using Transformer?

#### **OBSERVATIONS:**

ECE, MRCET **EDC Manual**

**EDC Manual** ECE, MRCET TITLE NAME DATE

# EXPERIMENT NO-7 SWITCHING CHARECTERISTICS TRANSISTOR

**AIM:** To obtain characteristics of a transistor as a switch.

**EQUIPMENT REQUIRED:** Multisim

THEORY:

Transistors are widely used in digital logic circuits and switching applications. In these applications the voltage levels periodically alternate between a "LOW" and a "HIGH" voltage, such as 0V and +5V. In switching circuits, a transistor is operated at cutoff for the OFF condition, and in saturation for the ON condition. The active linear region is passed through abruptly switching from cutoff to saturation or vice versa. In cutoff region, both the transistor junctions between Emitter and Base and the junction between Base and Collector are reverse biased and only the reverse current which is very small and practically neglected, flows in the transistor. In saturation region both junctions are in forward bias and the values of  $V_{ce}$  (sat) and  $V_{be}$  (sat) are small.

#### **PROCEDURE:**

- 1. Connect the circuit as per circuit diagram.

- 2. Obtain a constant amplitude square wave from function generator of 5V p-p and give the signal as input to the circuit.

- 3. Observe the output waveform and note down its voltage amplitude levels.

- 4. Draw the input and output waveforms

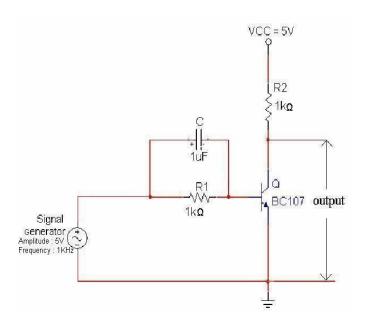

#### **CIRCUIT DIAGRAM:**

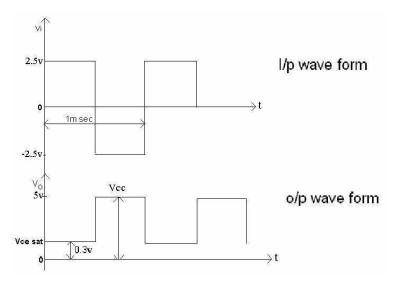

# Model graph

#### **THEORETICAL CALICULATIONS:**

When Vi= +2.5v, the transistor goes into saturation region.

So  $V_{O=}V_{ce sat=}0.3V$ .

When  $V_i$ =-2.5v, the transistor is in cutoff region so  $V_o$ =Vcc=5v

#### **PRECAUTIONS:**

- 1. Connections should be made carefully.

- 2. Verify the circuit before giving supply voltage.

- 3. Take readings without any parallax error.

#### **RESULT:**

### **QUESTION & ANSWERS:**

- 1. What are the limitations of transistor switch?

- 2. What is the turn on time of a transistor?

#### **Exercise Questions:**

- 1) For a C.E transistor circuits with  $V_{CC}=15V$  R<sub>C</sub>=1.5K $\Omega$ .Caculate the transistor power dissipation

- a) at cutoff and b) at saturation

R20 Autonomous II B. Tech II Semester **OBSERVATIONS:**

ECE, MRCET AC Manual TITLE NAME DATE

# EXPERIMENT NO-8 BISTABLE MULTIVIBRATOR

**Aim:** To observe the stable states voltages of Bi-stable Multivibrator.

**EQUIPMENT REQUIRED:** Multisim

THEORY:

The circuit diagram of a fixed bias Bi-stable multivibrator using transistors. The output of each amplifier is direct coupled to the input of the other amplifier. In one of the stable states transistor  $Q_1$  and  $Q_2$  is off and in the other stable state.  $Q_1$  is off and  $Q_2$  is on even though the circuit is symmetrical; it is not possible for the circuit to remain in a stable state with both the transistors conducting simultaneously and caring equal currents. The reason is that if we assume that both the transistors are biased equally and are carrying equal currents  $i_1$  and  $i_2$  suppose there is a minute fluctuation in the current  $i_1$ -let us say it increases by a small amount.

Then the voltage at the collector of  $q_1$  decreases. This will result in a decrease in voltage at the base of  $q_2$ . So  $q_2$  conducts less and  $i_2$  decreases and hence the potential at the collector of  $q_2$  increases. This result in an increase in the base potential of  $q_1$ . So  $q_1$  conducts still more and  $i_1$  is further increased and the potential at the collector of  $q_1$  is further decreased, and so on. So the current  $i_1$  keeps on increasing and the current  $i_2$  keeps on decreasing till  $q_1$  goes in to saturation and  $q_2$  goes in to cut-off. This action takes place because of the regenerative feed – back incorporated into the circuit and will occur only if the loop gain is greater than one.

#### **CIRCUIT DIAGRAM:**

#### PROCEDURE:

- 1. Connect the circuit as shown in figure.

- 2. Verify the stable state by measuring the voltages at two collectors by using multimeter.

- 3. Note down the corresponding base voltages of the same state (say state-1).

- 4. To change the state, apply negative voltage (say-2v) to the base of on transistor or positive voltage to the base of transistor (through proper current limiting resistance).

- 5. Verify the state by measuring voltages at collector and also note down voltages at each base.

# R20 Autonomous II B. Tech II Semester **PRECAUTIONS:**

- 1. Connections should be made carefully.

- 2. Note down the parameters carefully.

- 3. The supply voltage levels should not exceed the maximum rating of the transistor.

#### **RESULT:**

# **QUESTION & ANSWERS:**

- 1. What do you mean by a bistable circuit?

- 2. What are the other names of a bistable multivibrator?

- 3. What do you mean by triggering signal?

# **Exercise Questions:**

- 1) A self-biased binary uses n-p-n transistors have maximum values of  $V_{CE}$  (sat) =0.4V and  $V_{BE}$  (sat) = 0.8V and  $V_{BE}$  cutoff = 0V. The circuit parameters are  $V_{CC}$  = 15V,  $R_C$  = 1K $\Omega$ ,  $R_1$  = 6K $\Omega$ ,  $R_2$  = 15K $\Omega$  and  $R_F$  = 500 $\Omega$ .

- a) Find the stable-state currents and voltages.

# **OBSERVATIONS:**

ECE, MRCET AC Manual

ECE, MRCET AC Manual TITLE NAME DATE

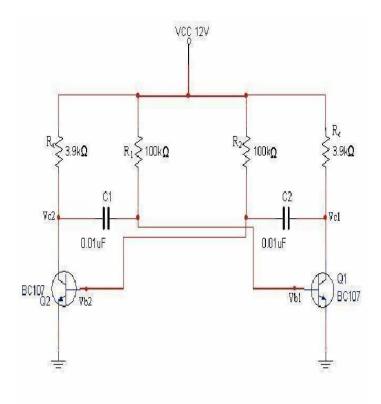

# EXPERIMENT NO-9 ASTABLE MULTIVIBRATOR

**AIM:** To Observe the ON & OFF states of Transistor in an Astable Multivibrator.

**EQUIPMENT REQUIRED:** Multisim

THEORY:

An Astable Multivibrator has two quasi stable states and tkeeps on switching between these two statesby itself. No external triggering signal is needed. The astable multivibrator cannot remain indefinitely in any one of the two states .The Two amplifier stages of an astable multivibrator are regenerative across coupled by Capacitors. The astable multivibrator may be to generate a square wave of period, 1.38RC

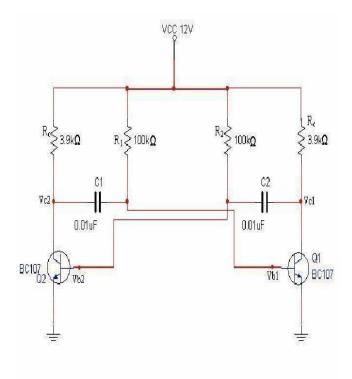

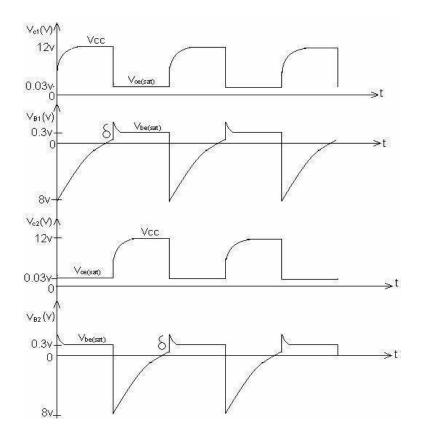

#### **CIRCUIT DIAGRAM**

#### PROCEDURE:

- 1. Calculate the theoretical frequency of oscillations of the circuit.

- 2. Connect the circuit as per the circuit diagram.

- 3 Observe the voltage wave forms at both collectors of two transistors simultaneously.

- 4. Observe the voltage wave forms at each base simultaneously with corresponding collector voltage.

- 5. Note down the values of wave forms carefully.

- 6. Compare the theoretical and practical values.

#### **CALCULATIONS:**

#### **THEORITICAL VALUES:**

$RC = R_1C_1 + R_2C_2$

Time Period, T = 1.368RC

Frequency, f = 1/T =

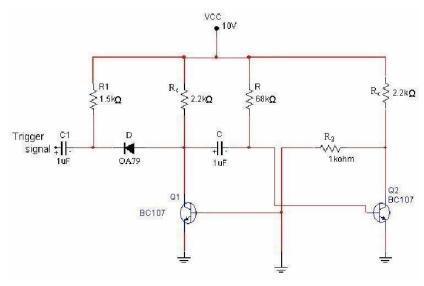

#### **MODEL WAVEFORMS**

#### PRECAUTIONS:

- 1. Connections should be made carefully.

- 2. Readings should be noted without parallax error.

#### **RESULT:**

# **VIVA QUESTIONS:**

- 1. Define stable state?

- 2. Define quasi stable state?

# **Exercise Questions:**

1) Design a collector coupled a stable multivibrator for the following specifications with Silicon transistor. IC (sat) = 10m A; hfe (min) = 20; VCC = 10V; pulse width=10 $\mu$ sec; duty Cycle=40%

#### **OBSERVATIONS:**

ECE, MRCET AC Manual TITLE NAME DATE

# EXPERIMENT NO-10 MONOSTABLE MULTIVIBRATOR

**AIM:** To observe the stable state and quasi stable state voltages in monostable Multivibrator.

**EQUIPMENT REQUIRED: Multisim**

#### THEORY:

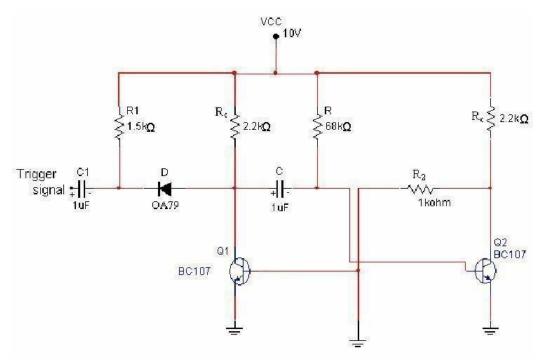

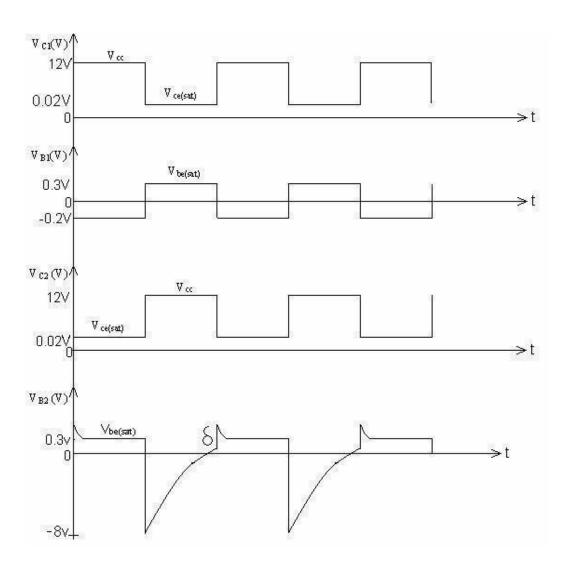

A monostable multivibrator on the other hand compared to astable, bistable has only one stable state, the other state being quasi stable state. Normally the multivibrator is in stable state and when an externally triggering pulse is applied, it switches from the stable to the quasi stable state. It remains in the quasi stable state for a short duration, but automatically reverse switches back to its original stable state without any triggering pulse. The monostable multivibrator is also referred as 'one shot' or 'uni vibrator' since only one triggering signal is required to reverse the original stable state. The duration of quasi stable state is termed as delay time (or) pulse width (or) gate time. It is denoted as't'.

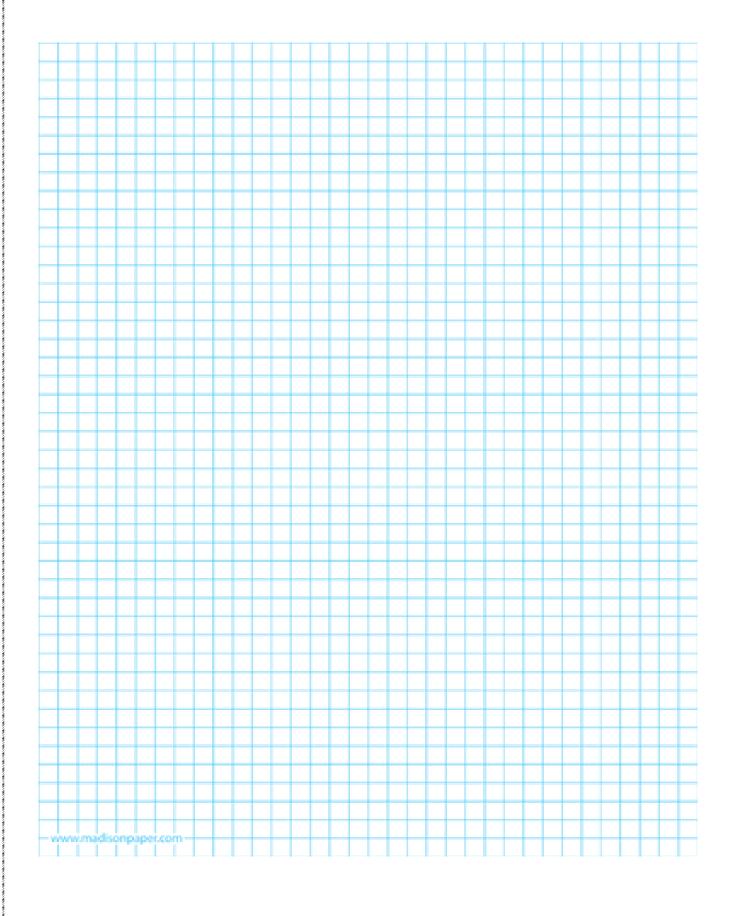

#### **CIRCUIT DIAGRAM:**

#### PROCEDURE:

- 1. Connect the circuit as per the circuit diagram.

- 2. Verify the stable states of Q<sub>1</sub> and Q<sub>2</sub>

- 3. Apply the square wave of 2v p-p, 1KHz signal to the triggercircuit.

- 4. Observe the wave forms at base of each transistor simultaneously.

- 5. Observe the wave forms at collectors of each transistor simultaneously.

- 6. Note down the parameters carefully.

- 7. Note down the time period and compare it with theoretical values.

- 8. Plot wave forms of  $V_{b1}$ ,  $V_{b2}$ ,  $V_{c1}$  &  $V_{c2}$  with respect to time.

**Theoretical Values:**

Time Period, T = 0.693RC

Frequency, f = 1/T =

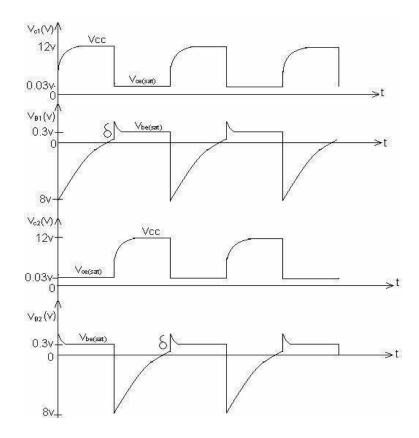

# **MODEL WAVEFORMS:**

# **PRECAUTIONS:**

- 1. Connections should be made carefully.

- 2. Note down the parameters without parallax error.

- 3. The supply voltage levels should not exceed the maximum rating of the transistor.

# **RESULT:**

# **QUESTION & ANSWERS:**

- 1. What are the other names of Mono Stable multivibrator?

- 2. Which type of triggering is used in mono stable multi vibrator?

- 3. Define transition time?

## **Exercise Questions:**

1) Design and draw a collector-coupled ONE-SHOT using silicon npn transistors with h  $_{FE}$  (min) = 20. In stable State, the transistor in cut-off has V  $_{BE}$  = -1V and the transistor in saturation has base current, I  $_B$  which is 50% excess of the I  $_B$  (min) value. Assume V CC = 8V, I  $_C$  (sat) =2mA, delay time = 2.5ms &; R  $_1$  = R 2. Find R  $_C$ , R, R  $_1$ , C and V  $_B$ .

#### **OBSERVATIONS:**

# PART-II

# EXPERIMENT NO: 1 CLASS-A POWER AMPLIFIER

#### AIM:

To design a series fed class-A power amplifier in order to achieve max output ac power and efficiency.

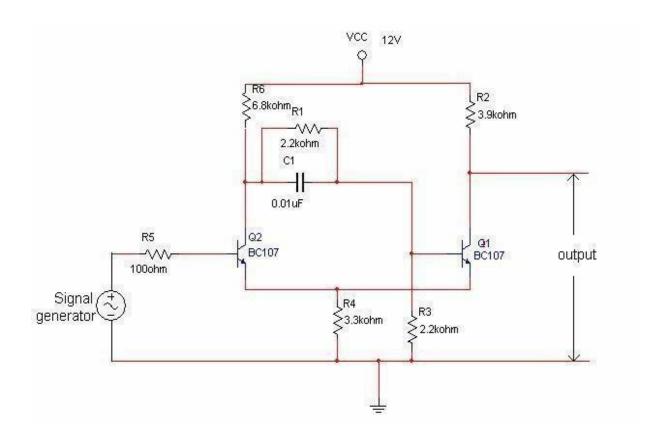

**EQUIPMENT REQUIRED:** Class A amplifier kit, Function generator, CRO, connecting probes. **CIRCUIT DIAGRAM:**

#### THEORY:

The above circuit is called as "series fed" because the load RL is connected in series with transistor output. It is also called as direct coupled amplifier.

ICQ = Zero signal collector current

VCEQ = Zero signal collector to emitter voltage

Power amplifiers are mainly used to deliver more power to the load. To deliver more power it requires large input signals, so generally power amplifiers are preceded by a series of voltage amplifiers. In class-A power amplifiers, Q-point is located in the middle of DC-load line. So output current flows for complete cycle of input signal. Under zero signal condition, maximum power dissipation occurs across the transistor. As the input signal amplitude increases power dissipation reduces The maximum theoretical efficiency is 25%.

#### APPLICATIONS:

This is used for low power linear applications in audio and wideband RF range, where high efficiency is not required.

#### **EXTENSIONS:**

In series fed class-A power amplifier we have calculated the efficiency i.e. how efficiently DC- power is converted into AC-power depending on the magnitude of input signal. Once we design a power amplifier for a particular efficiency, the circuit will not give that efficiency to all its

input signals of different amplitudes. Hence, depending on the input signal we have to choose Vcc to obtain a particular efficiency. By employing Transformer coupling, efficiency can be improved to 50%. The experiment is conducted using low power transistors like BC107, SL100 only to get familiarity in biasing and measurement. Actual power amplifiers operate at 1 watt to 100 watts. This will call for operating transistors high current and small value resistors of greater than 1/4 to 1 watt which are used in the laboratory. Actual power amplifiers use heat sinks on the transistors.

#### PROCEDURE:

- 1. Place all the necessary components required for the design of the Complementary symmetry Class A Power amplifier circuit i.e. Resistors, Capacitors, Diodes, Transistors, Voltage sources, Power sources, Ground etc on the designwindow.

- 2. Connect all the components by proper wiring and also assure that nodes are formed at the interconnection points.

- 3. Connect the channel of the Oscilloscope to the output of the circuit and by using the simulation switch and check output waveform.

- 4. To obtain the netlist, go to transfer port netlist and save the netlist in a text file. On opening the text file from the saved location, a netlist is obtained containing the specifications of all the used components used in the design of the circuit.

#### **OBSERVATIONS:**

Efficiency is defined as the ratio of AC output power to DC input power

DC input power =  $Vcc \times I_{CQ}$

AC output power =  $V_{P-P}^2 / 8R_L$

#### **CALCULATIONS:**

Under zero signal condition:

$Vcc = I_BR_B + V_{BE}$

$I_{BQ} = (V_{CC} - V_{BE}) / R_B$

$I_{CQ} = \beta \times I_{BQ}$

$V_{CE} = V_{CC} - I_{C}R_{C}$

#### **EXPECTED GRAPH:**

Vin=1V<sub>p-p</sub>

| <b>RESUL</b> | T: |

|--------------|----|

|              |    |

| 1. The maximum input signal amplitude which produces undistorted output signal is |                                           |  |  |  |

|-----------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| 2. The practical efficiency of the circuit is                                     |                                           |  |  |  |

| 3. The efficiency observed is                                                     | against theoretical maximum of 25%, Since |  |  |  |

#### **QUESTIONS:**

- 1. Differentiate between voltage amplifier and power amplifier

- 2. Why power amplifiers are considered as large signal amplifier?

- 3. When does maximum power dissipation happen in thiscircuit?

- 4. What is the maximum theoretical efficiency?

- 5. Sketch wave form of output current with respective input signal.

- 6. What are the different types of class-A power amplifiers available?

- 7. What is the theoretical efficiency of the transformer coupled class-A power amplifier?

- 8. What is difference in AC, DC load line?

- 9. How do you locate the Q-point?

- 10. What are the applications of class-A power amplifier?

#### **Exercise Question:**

1. Try to increase the efficiency of Class A power amplifier using Transformer?

#### **OBSERVATIONS:**

ECE, MRCET AC Manual

ECE, MRCET AC Manual TITLE NAME DATE

#### EXPERIMENT NO: 2 CLASS B AMPLIFIER

#### AIM:

To find the efficiency of a Complementary symmetry Class B Power Amplifier.

#### **SOFTWARE REQUIRED:** Multisim

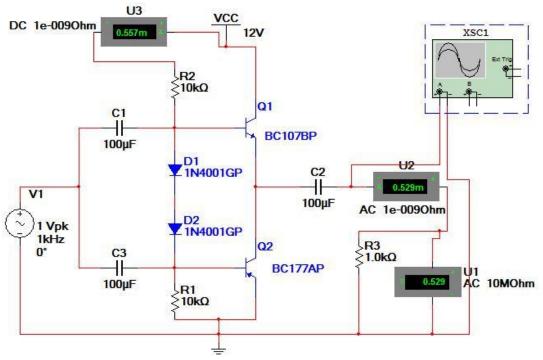

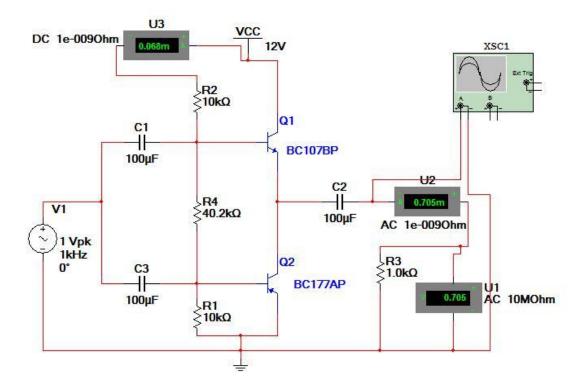

#### **CIRCUIT DIAGRAM:**

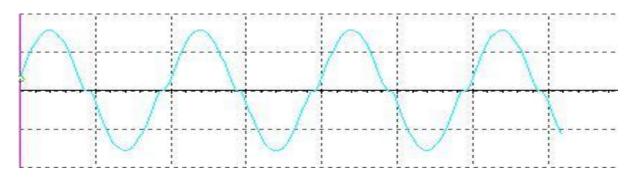

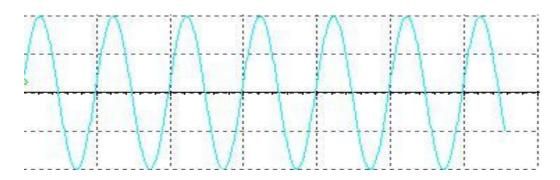

Fig1: Complementary symmetry Class B Power Amplifier Circuit With crossover distortion

Fig 2: Output waveform of Complementary symmetry Class B Power Amplifier Circuit with crossover distortion

#### THEORY:

The Class B amplifier circuit above uses complimentary transistors for each half of the waveform and while Class B amplifiers have a much high efficiency than the Class A types, one of the main disadvantages of class B type push-pull amplifiers is that they suffer from an effect known commonly as Crossover Distortion.

It takes approximately 0.7 volts (measured from base to emitter) to get a bipolar transistor to start conducting. In a class B amplifier, the output transistors are not "pre-biased" to an "ON" state of operation. This means that the part of the output waveform which falls below this 0.7 volt window will not be reproduced accurately as the transition between the two transistors (when they are switching over from one to the other), the transistors do not stop or start conducting exactly at the zero crossover point even if they are specially matched pairs.

The output transistors for each half of the waveform (positive and negative) will each have a 0.7 volt area in which they will not be conducting resulting in both transistors being "OFF" at the same time.

A simple way to eliminate crossover distortion in a Class B amplifier is to add two small voltage sources to the circuit to bias both the transistors at a point slightly above their cut-off point.. However, it is impractical to add additional voltage sources to the amplifier circuit so pn-junctions are used to provide the additional bias in the form of silicon diodes.

We know that we need the base-emitter voltage to be greater than 0.7v for a silicon bipolar transistor to start conducting, so if we were to replace the two voltage divider biasing resistors connected to the base terminals of the transistors with two silicon Diodes, the biasing voltage applied to the transistors would now be equal to the forward voltage drop of the diode. These two diodes are generally called Biasing Diodes or Compensating Diodes and are chosen to match the characteristics of the matching transistors.

#### **PROCEDURE:**

- 1. Connect the trainer kit as per Circuit Diagram.

- 2. Place all the necessary components required for the design of the Complementary symmetry Class B Power amplifier circuit i.e Resistors, Capacitors, Diodes, Transistors, Voltage sources, Power sources, Ground etc on the design window.

- 3. Connect all the components by proper wiring and also assure that nodes are formed at the interconnection points.

- 4. Connect the channel of the Oscilloscope to the output of the circuit and by using the simulation switch and check output waveform.

- 5. To obtain the netlist, go to transfer----- export netlist and save the netlist in a text file. On opening the text file from the saved location, a netlist is obtained containing the specifications of all the used components used in the design of the circuit.

#### THEORETICAL CALCULATIONS:

$$I_{CQ} = \frac{V_{CC}/R_L}{P_{in} (d.c) = \frac{V_{CC}}{2\pi} I_{CQ}}$$

$$\frac{V_{CC} * V_{CC}}{2\pi R_L} = \frac{(V_{CC})^2}{2\pi R_L}$$

Po(a.c) =

$$\frac{(Vmax - Vmin)*(Imax - Imin)}{8}$$

$$(I_{\text{max}} - I_{\text{min}}) = \frac{V_{CC}}{R_L}$$

$$(Vmax - Vmin) = VCC$$

Po(a.c)

$$=\frac{V_{CC}*V_{CC}}{8R_L} = \frac{V_{CC}^2}{8R_L}$$

% of efficiency =

$$\frac{\frac{\text{Po(a.c)}}{\text{Pin(d.c-*}100 = }}{\frac{\text{V}_{CC}^2}{\text{V}_{CC}^2}/\frac{1}{2\pi R_L}} = \frac{\pi}{4*100 = 78.5\%}$$

#### **PRACTICAL CALCULATIONS:**

% of efficiency

$$= \frac{Po(a.c)}{Pin(dc)} *_{100}$$

$$\eta = Pac *_{100}$$

$$Pdc$$

$$\eta = \frac{\text{(Vac * Iac)}}{\text{(Vcc * Idc)}}$$

#### **RESULT:**

The efficiency of Class B Power Amplifier is \_\_\_\_\_%.

#### **QUESTIONS:**

- 1. Explain complementary and symmetry concept?

- 2. What is the conduction angle in class B operation?

Malla Reddy College of Engineering and Technology(MRCET)

| TITLE | TITLE |  |

|-------|-------|--|

| NAME  | DATE  |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

|       |       |  |

Malla Reddy College of Engineering and Technology(MRCET)

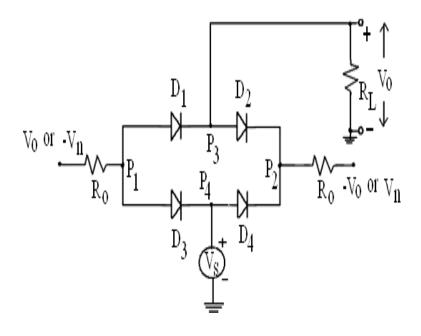

#### **EXPERIMENT NO: 3**

#### **CLASS B COMPLEMENTARY SYMMETRY AMPLIFIER**

#### AIM:

To find the efficiency of a Complementary symmetry Class B Power Amplifier.

**EQUIPMENT REQUIRED:** Class A amplifier kit, Function generator, CRO, connecting probes.

#### **CIRCUIT DIAGRAM:**

Fig 3: Class B Power Amplifier circuit where crossover distortion is eliminated

Fig 4: Output waveform of Complementary symmetry Class B Power Amplifier circuit where crossover distortion is eliminated

#### THEORY:

#### R20 Autonomous II B. Tech II Semester

The Class B amplifier circuit above uses complimentary transistors for each half of the waveform and while Class B amplifiers have a much high efficiency than the Class A types, one of the main disadvantages of class B type push-pull amplifiers is that they suffer from an effect known commonly as Crossover Distortion.

It takes approximately 0.7 volts (measured from base to emitter) to get a bipolar transistor to start conducting. In a class B amplifier, the output transistors are not "pre-biased" to an "ON" state of operation. This means that the part of the output waveform which falls below this 0.7 volt window will not be reproduced accurately as the transition between the two transistors (when they are switching over from one to the other), the transistors do not stop or start conducting exactly at the zero crossover point even if they are specially matched pairs.

The output transistors for each half of the waveform (positive and negative) will each have a 0.7 volt area in which they will not be conducting resulting in both transistors being "OFF" at the same time.

A simple way to eliminate crossover distortion in a Class B amplifier is to add two small voltage sources to the circuit to bias both the transistors at a point slightly above their cut-off point.. However, it is impractical to add additional voltage sources to the amplifier circuit so pn-junctions are used to provide the additional bias in the form of silicon diodes.

We know that we need the base-emitter voltage to be greater than 0.7v for a silicon bipolar transistor to start conducting, so if we were to replace the two voltage divider biasing resistors connected to the base terminals of the transistors with two silicon Diodes, the biasing voltage applied to the transistors would now be equal to the forward voltage drop of the diode. These two diodes are generally called Biasing Diodes or Compensating Diodes and are chosen to match the characteristics of the matching transistors.

#### **PROCEDURE:**

- 1. Connect the Trainer Kit.

- 2. Place all the necessary components required for the design of the Complementary symmetry Class B Power amplifier circuit i.e Resistors, Capacitors, Diodes, Transistors, Voltage sources, Power sources, Ground etc on the design window.

- 3. Connect all the components by proper wiring and also assure that nodes are formed at the interconnection points.

- 4. Connect the channel of the Oscilloscope to the output of the circuit and by using the simulation switch and check output waveform.

- 5. To obtain the netlist, go to transfer----- export netlist and save the netlist in a text file. On opening the text file from the saved location, a netlist is obtained containing the specifications of all the used components used in the design of the circuit.

#### **OBSERVATIONS:**

#### THEORETICAL CALCULATIONS:

$$I_{CQ} = \frac{V_{CC}}{R_L}$$

$$P_{in} (d.c) = \frac{V_{CC}}{2\pi} I_{CQ}$$

R20 Autonomous II B. Tech II Semester

$$P_{in}(d.c) = \frac{V_{CC} * V_{CC}}{2\pi R_L} = \frac{(V_{CC})^2}{2\pi R_L}$$

Po(a.c) =

$$\frac{(Vmax - Vmin)*(Imax - Imin)}{8}$$

$$(I_{\text{max}} - I_{\text{min}}) = \frac{V_{CC}}{R_L}$$

$$(Vmax - Vmin) = VCC$$

Po(a.c)

$$= \frac{V_{CC} * V_{CC}}{8R_L} = \frac{V_{CC}^2}{8R_L}$$

% of efficiency =

$$\frac{\frac{\text{Po(a.c)}}{\text{Pin(d.c-*}100 = }}{\frac{\text{V}_{CC}^2}{2\pi R_L}} = \frac{\frac{\pi}{4} *100 = 78.5\%}{ *100}$$

#### **PRACTICAL CALCULATIONS:**

% of efficiency

$$= \frac{Po(a.c)}{Pin(dc)} *_{100}$$

$$\eta = Pac *_{100}$$

$$Pdc$$

$$\eta = (\text{Vac} * \text{Iac}) *100$$

$$(\text{Vcc} * \text{Idc})$$

#### **RESULT:**

The efficiency of Complementary Symmetry Class B Power Amplifier is \_\_\_\_\_%.

#### **QUESTIONS:**

- 1. Explain complementary and symmetry concept?

- 2. What is the conduction angle in class B operation?

- 3. What is the efficiency of class B power amplifier?

- 4. What is the formula for output power in class B power amplifier

Analog Circuits Lab Manual R20 Autonomous II B. Tech II Semester

Analog Circuits Lab Manual R20 Autonomous II B. Tech II Semester TITLE NAME DATE

#### **EXPERIMENT NO: 4**

#### **CLASS C POWER AMPLIFIER**

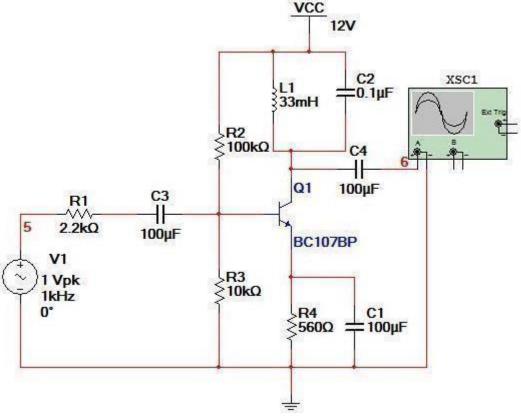

To determine the resonant frequency and bandwidth of a tuned amplifier.

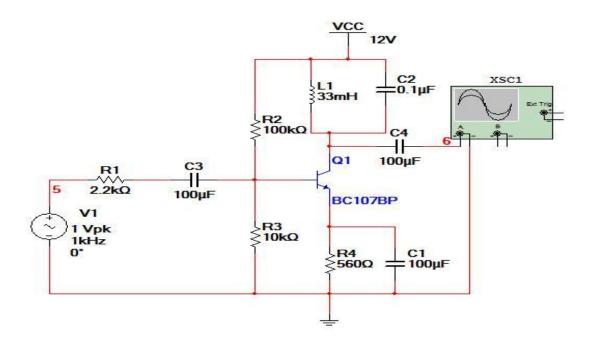

**EQUIPMENT REQUIRED**: Tuned voltage amplifier kit, Function generator, CRO, connecting probes. **CIRCUIT DIAGRAM**:

#### THEORY:

A tuned amplifier is one which uses one or more parallel tuned circuit as the load impedance. A tuned amplifier is capable of amplifying a signal over a narrow band of frequencies. The gain of a tuned amplifier is maximum at the resonant frequency and it falls sharply below and above the resonant frequency. At the resonant frequency, the inductive and capacitive reactances are equal.

$$f_o = \frac{1}{2\pi\sqrt{LC}}$$

#### **PROCEDURE:**

- 1. Apply an input voltage of 1vp -p at 1 kHz from the function generator at the input terminals of the Tuned voltage amplifier and observe the signal on the CRO.

- 2. Connect the output of the circuit to the channel of the CRO.

- Note down the output voltage.

- 4. Calculate the voltage gain in dB using the formula Av=20 log (Vo/Vi).

#### **OBSERVATION TABLE:**

| S.NO | FREQUENCY(Hz) | OUTPUT<br>VOLTAGE<br>(Vo) | VOLTAGE<br>GAIN<br>(Avf=Vo/Vi) | GAIN (dB)<br>Avf=20 log<br>(Vo/Vi). |

|------|---------------|---------------------------|--------------------------------|-------------------------------------|

|      |               |                           |                                |                                     |

|      |               |                           |                                |                                     |

|      |               |                           |                                |                                     |

|      |               |                           |                                |                                     |

Bandwidth of the CE amplifier =  $f_h$ - $f_l$  HZ

#### **EXPECTED GRAPH:**

| •                  | n isdB, the resonant frequency isHz and bandwidth is<br>dz of the Tuned Amplifier. |

|--------------------|------------------------------------------------------------------------------------|

| QUESTIONS:         |                                                                                    |

| 1. What is a       | a tuned amplifier?                                                                 |

| 2. What is t       | the formula for resonant frequency of a tuned amplifier?                           |

|                    | the difference between single, double and stagger tuned amplifiers?                |

| Exercise Question: |                                                                                    |

1. By changing the tuned circuit components set the center frequency to 10 Khz

### OBSERVATIONS:

ECE, MRCET AC Manual

ECE, MRCET AC Manual TITLE NAME DATE

## EXPERIMENT NO:5 SINGLE TUNED VOLTAGE AMPLIFIER

#### AIM:

To determine the resonant frequency and bandwidth of a tuned amplifier.

**EQUIPMENT REQUIRED:** Tuned voltage amplifier kit, Function generator, CRO, connecting probes.

#### **CIRCUIT DIAGRAM:**

#### THEORY:

A tuned amplifier is one which uses one or more parallel tuned circuit as the load impedance. A tuned amplifier is capable of amplifying a signal over a narrow band of frequencies. The gain of a tuned amplifier is maximum at the resonant frequency and it falls sharply below and above the resonant frequency. At the resonant frequency, the inductive and capacitive reactances are equal.

$$f_0=1/2\pi V(LC)$$

#### **PROCEDURE:**

- 1. Apply an input voltage of 1vp -p at 1 kHz from the function generator at the input terminals of the Tuned voltage amplifier and observe the signal on the CRO.

- 2. Connect the output of the circuit to the channel of the CRO.

- 3. Note down the output voltage.

- 4. Calculate the voltage gain in dB using the formula Av=20 log (Vo/Vi).

## R20 Autonomous II B. Tech II Semester **OBSERVATION TABLE**:

| S.NO | FREQUENCY(Hz) | GAIN(dB) |

|------|---------------|----------|

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

|      |               |          |

Bandwidth of the Tuned amplifier= $f_h$ - $f_l$  Hz

#### **EXPECTED GRAPH:**

#### Frequency response and phase response graphs

| RESULT: The maximum gain is Tuned Amplifier. | _dB, the resonant frequency is | Hz and bandwidth is | Hz of the |

|----------------------------------------------|--------------------------------|---------------------|-----------|

| QUESTIONS:                                   | rr. a                          |                     |           |

- 1. What is a tuned amplifier?

- 2. What is the formula for resonant frequency of a tuned amplifier?

- 3. What is the difference between single, double and stagger tuned amplifiers?

ECE, MRCET AC Manual

ECE, MRCET AC Manual TITLE NAME DATE

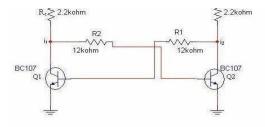

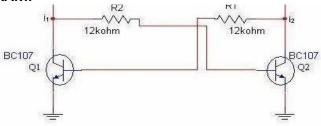

## EXPERIMENT NO-6 BISTABLE MULTIVIBRATOR

**Aim:** To observe the stable states voltages of Bi-stable Multivibrator.

## **Apparatus required**

| S.No | Name of the               |                |          |

|------|---------------------------|----------------|----------|

|      | Component/Equipment       | Specifications | Quantity |

| 1    | Resistors                 | 2.2ΚΩ, 12ΚΩ    | 2        |

| 2    | CRO                       | 20MHz          | 1        |

| 3    | Function generator        | 1MHz           | 1        |

| 4    | Connecting Wires          | -              | As       |

|      |                           |                | Required |

| 6    | DC Regulated power supply | 0-30V,1A       | 1        |

| 8    | Transistor                | BC 107         | 2        |

#### THEORY:

The circuit diagram of a fixed bias Bi-stable multivibrator using transistors. The output of each amplifier is direct coupled to the input of the other amplifier. In one of the stable states transistor  $Q_1$  and  $Q_2$  is off and in the other stable state.  $Q_1$  is off and  $Q_2$  is on even though the circuit is symmetrical; it is not possible for the circuit to remain in a stable state with both the transistors conducting simultaneously and caring equal currents. The reason is that if we assume that both the transistors are biased equally and are carrying equal currents  $i_1$  and  $i_2$  suppose there is a minute fluctuation in the current  $i_1$ -let us say it increases by a small amount.

Then the voltage at the collector of  $q_1$  decreases. This will result in a decrease in voltage at the base of  $q_2$ . So  $q_2$  conducts less and  $i_2$  decreases and hence the potential at the collector of  $q_2$  increases. This result in an increase in the base potential of  $q_1$ . So  $q_1$  conducts still more and  $i_1$  is further increased and the potential at the collector of  $q_1$  is further decreased, and so on. So the current  $i_1$  keeps on increasing and the current  $i_2$  keeps on decreasing till  $q_1$  goes in to saturation and  $q_2$  goes in to cut-off. This action takes place because of the regenerative feed – back incorporated into the circuit and will occur only if the loop gain is greater than one.

#### **CIRCUIT DIAGRAM:**

#### PROCEDURE:

#### R20 Autonomous II B. Tech II Semester

- 1. Connect the circuit as shown in figure.

- 2. Verify the stable state by measuring the voltages at two collectors by using multimeter.

- 3. Note down the corresponding base voltages of the same state (say state-1).

- 4. To change the state, apply negative voltage (say-2v) to the base of on transistor or positive voltage to the base of transistor (through proper current limiting resistance).

- 5. Verify the state by measuring voltages at collector and also note down voltages at each base.

#### PRECAUTIONS:

- 1. Connections should be made carefully.

- 2. Note down the parameters carefully.

- 3. The supply voltage levels should not exceed the maximum rating of the transistor.

#### **RESULT:**

#### **QUESTION & ANSWERS:**

- 1. What do you mean by a bistable circuit?

- 2. What are the other names of a bistable multivibrator?

- 3. What do you mean by triggering signal?

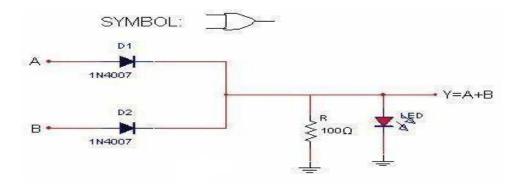

### **Exercise Questions:**